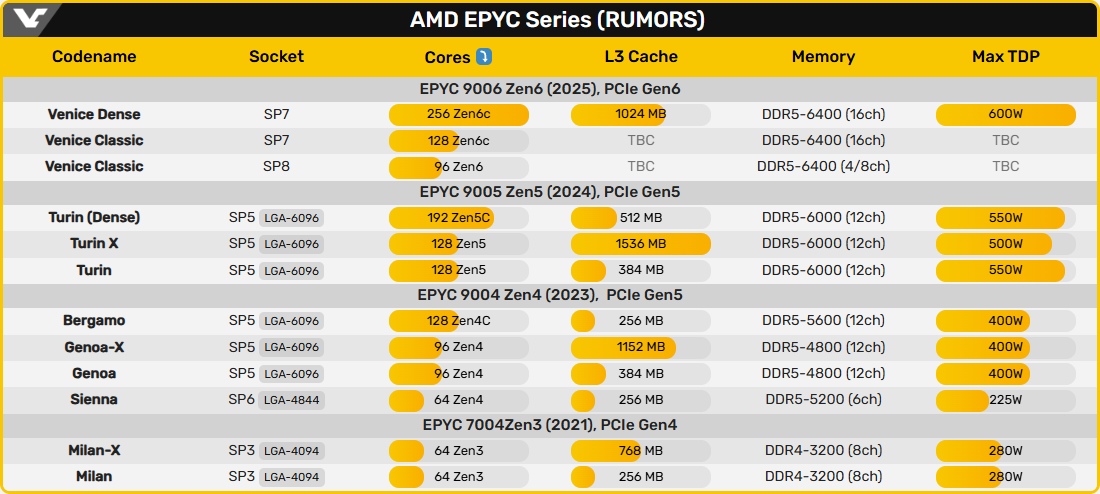

Від неофіційних джерел надійшли нові подробиці про наступне покоління серверних процесорів AMD EPYC, відоме під кодовим ім’ям Venice. У цих CPU компанія перейде на мікроархітектури Zen 6 і Zen 6c, а для їхнього виробництва буде використана 2‑нм технологія TSMC, чим уже встигла похвалитися голова «червоного» чипмейкера.

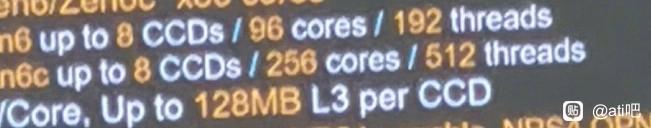

Свіжі витоки інформації розкривають деякі важливі особливості майбутніх CPU EPYC 9006. Зокрема, підтверджується використання восьми мікросхем Core Complex Die (CCD) з x86-ядрами. Це означає, що процесори з архітектурою Zen 6 завдяки 12-ядерним чиплетам CCD зможуть запропонувати до 96 ядер/192 потоків. В той самий час CPU Zen 6c отримають 32-ядерні чиплети, тобто в їхньому арсеналі буде 256 ядер/512 потоків.

У документах AMD також згадується до 128 МБ кеш-пам’яті третього рівня в одній мікросхемі Core Complex Die. Тобто за наявності восьми чиплетів CCD сумарний обсяг L3-кешу в таких процесорів складе 1 ГБ. Раніше для досягнення таких показників «червоним» доводилося використовувати технологію 3D V‑Cache.

Разом із новими процесорами дебютує серверна платформа Socket SP7, яка принесе підтримку 16-канальної оперативної пам’яті DDR5. Для CPU в цьому конструктивному виконанні буде характерний TDP до 600 Вт. AMD також готує простішу платформу Socket SP8. Вона підтримуватиме 96-ядерні процесори Zen 6 з рівнем TDP близько 350–400 Вт та, ймовірно, 8‑канальну пам’ять DDR5.

Офіційні подробиці про серверні чипи AMD EPYC 9006 (Venice), на думку закордонних колег, компанія може розкрити на презентації Advancing AI в червні.

Що стосується споживчих CPU Zen 6, то вони теж повинні перейти на використання 12-ядерних мікросхем CCD. Завдяки цьому майбутні топові процесори для настільних ПК отримають 24-ядерну/48-потокову конфігурацію. Сподіватимемося, що десктопні процесори Zen 6 продовжать використовувати платформу AMD AM5.

Джерела:

WCCFTech

VideoCardz