Специалисты компаний Toshiba и Western Digital совместно разработали 128-слойные микросхемы флэш-памяти 3D NAND TLC ёмкостью 512 Гбит (64 Гбайт), что на 33% выше чем у предшествующей 96-слойной памяти. В номенклатуре Toshiba этот чип будет называться BiCS-5 (BiCS-4 — 96-слойная, а BiCS-3 — 64-слойная флэш-памяти).

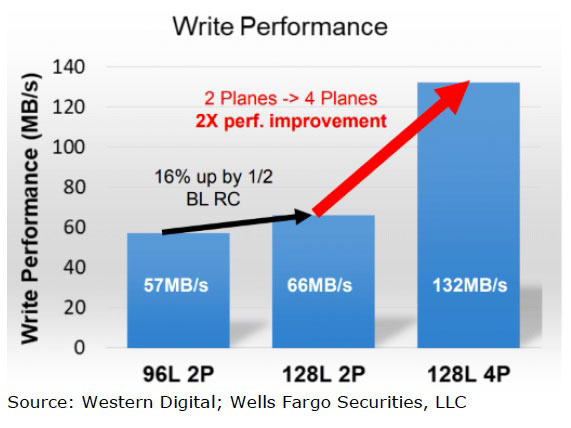

Сообщается, что кристалл BiCS-5 имеет компоновку с четырьмя отдельными секциями или плоскостями (planes), к каждой из которых можно получить независимый доступ. Для сравнения, микросхемы BiCS-3 и BiCS-4 использовали двухплоскостную структуру. В абсолютных значениях это позволило удвоить скорость записи на канал более чем в два раза: с 57 Мбайт/с до 132 Мбайт/с.

Кроме того, в новых микросхемах применяется конструкция Circuit-under-Array (CuA), которая подразумевает расположение логических управляющих схем в нижней плоскости. Благодаря этому размеры кристалла уменьшаются на 15% по сравнению с чипами без CuA.

Также инженерами компаний было принято решение осуществлять доступ к данным страницами по 4 Кбайт для снижения энергопотребления. В существующих накопителях используются страницы по 16 Кбайт.

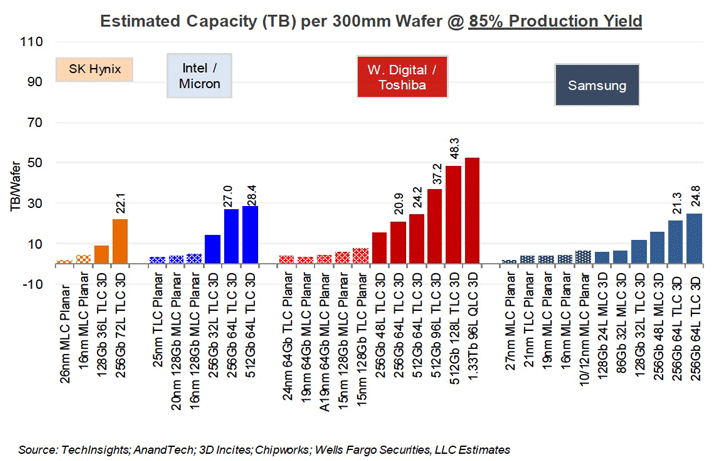

Старший аналитик Wells Fargo Аарон Рэйкерс (Aaron Rakers) утверждает, что Toshiba и Western Digital смогут предложить самую высокую в индустрии плотность чипа с 85-процентным выходом годных пластин. Коммерческое использование 128-слойных микросхем 3D NAND может начаться уже в следующем году.

Источник:

Blocks&Files