Терминология

Ниже приведен список технических терминов, относящихся к разгону памяти с процессором Ryzen. Последний использует стандартную архитектуру памяти DDR4, поэтому вы можете быть знакомы с некоторыми из этих терминов. Некоторые другие термины являются новыми и характерными для UEFI материнских плат платформы AM4.

SOC Voltage — напряжение контроллера памяти. Предел 1,2 В.

DRAM Boot Voltage — напряжение, на котором происходит тренировка памяти при запуске системы. Лимит: до 1,45–1,50 В.

VDDP Voltage — это напряжение для транзистора, который конфигурирует содержимое оперативной памяти. Лимит: до 1,1 В.

VPP (VPPM) Voltage — напряжение, которое определяет надежность доступа к строке DRAM.

CLDO_VDDP Voltage — напряжение для DDR4 PHY на SoC. DDR4 PHY, или интерфейс физического уровня DDR4, преобразует информацию, которая поступает из контроллера памяти в формат, понятный модулям памяти DDR4.

Несколько нелогично, что снижение CLDO_VDDP часто может быть более выгодным для стабильности, чем повышение. Опытные оверклокеры также должны знать, что изменение CLDO_VDDP может сдвинуть или устранить дыры в памяти. Небольшие изменения в CLDO_VDDP могут иметь большой эффект, и для CLDO_VDDP нельзя установить значение, превышающее VDIMM –0,1 В. Tсли вы измените это напряжение, то потребуется холодная перезагрузка. Лимит: 1,05 В.

Vref Voltage — источник опорного напряжения оперативной памяти. «Настройка» взаимосвязи контроллера памяти и модуля памяти в зависимости от уровня напряжения, которое рассматривается как «0» или «1»; то есть напряжения, найденные на шине памяти ниже MEMVREF, должны рассматриваться как «0», а напряжения выше этого уровня должны считаться «1». По умолчанию этот уровень напряжения составляет половину VDDIO (около 0,500x). Некоторые материнские платы позволяют пользователю изменять это соотношение, обычно двумя способами: (1) «DRAM Ctrl Ref Voltage» (для линий управления с шины памяти; официальное название JEDEC для этого напряжения — VREFCA) и (2) «DRAM Ctrl Data Ref Voltage» (для строк данных с шины памяти; официальное название JEDEC — VREFDQ). Эти параметры настроены как множитель.

VTT DDR Voltage — напряжение, используемое для управления сопротивлением шины, чтобы достигнуть высокой скорости и поддержать целостность сигнала. Это осуществляется с помощью резистора параллельного прерывания.

PLL Voltage — определяет напряжение питания системы Фазовой АвтоПодстройки Частоты (ФАПЧ или PLL — Phase Locked Loop) и является актуальной лишь для повышения стабильности во время разгона системы с помощью BCLK. Лимит: 1,9 В.

CAD_BUS — САПР командной и адресной шины. Для тех, кто может тренировать память на высоких частотах (>=3466 МГц), но не может стабилизировать ее из-за проблем с сигнализацией. Я предлагаю вам попробовать уменьшить токи привода, связанные с «Командой и адресом» (увеличив сопротивление).

CAD_BUS Timings — задержка трансивера. Значения являются битовой маской (грубой / точной задержки). Аналог RTL/IOL в исполнении AMD. Имеют огромное влияние на тренировку памяти.

procODT — значение сопротивления, в омах, который определяет, как завершенный сигнал памяти терминируется. Более высокие значения могут помочь стабилизировать более высокие скорости передачи данных. Ограничение: нет.

RTT (время приема-передачи) — это время, затраченное на отправку сигнала, плюс время, которое требуется для подтверждения, что сигнал был получен. Это время задержки, следовательно, состоит из времени передачи сигнала между двумя точками. Настройка, которая отвечает за оптимизацию целостности сигнала. DRAM предлагает диапазон значений сопротивления нагрузки. Конкретное сопротивление приемника выводов DQ, представленное интерфейсу, выбирается комбинацией начальной конфигурации микросхемы и рабочей команды DRAM, если включено динамическое завершение на кристалле.

Geardown Mode — позволяет памяти уменьшать эффективную скорость передачи данных на шинах команд и адресов.

Power Down Mode — может незначительно экономить энергию системы за счет более высокой задержки DRAM, переводя DRAM в состояние покоя после периода бездействия.

BankGroupSwap (BGS) — настройка, которая изменяет способ назначения приложениям физических адресов в модулях памяти. Цель этого регулятора — оптимизировать выполнение запросов к памяти, учитывая архитектуру DRAM и тайминги памяти. Теория гласит, что переключение этого параметра может сместить баланс производительности в пользу игр или синтетических приложений.

Игры получают ускорение при отключенной BGS, а пропускная способность памяти AIDA64 была выше при включенной BGS.

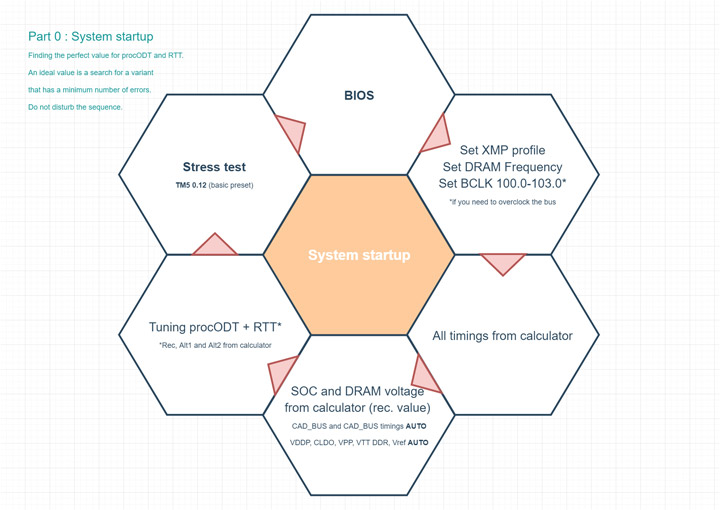

Алгоритм настройки системы

Инструмент, который будет нам помогать с рекомендациями — DRAM Calculator for Ryzen. Самый главный, фундаментальный шаг — это запуск системы на определенной частоте, которую мы хотим получить. Для этого нам потребуется вручную установить такие настройки в UEFI: профиль XMP памяти (он может называться по-разному, смысл от этого не меняется), частоту для оперативной памяти (которую мы хотим получить), установить частоту BCLK (если присутствует такая настройка в прошивке), тайминги (которые рекомендует калькулятор), напряжение для SOC и DRAM (рекомендации калькулятора) и procODT + RTT (NOM, WR и PARK). Не забывайте про важный нюанс, что материнская плата или оперативная память может не справиться с вашими амбициями, потому советую посетить страницу поддержки вашей материнской платы и посмотреть QVL-список, в котором будут указаны частоты, на которых плата в заводских условиях функционировала без ошибок. Эта частота и будет нашей отправной точкой. Зачастую это 3000–3200 МГц.

Параметры procODT + RTT (NOM, WR и PARK) мы будем подбирать так, чтоб система имела минимальное кол-во ошибок. Тестовый пакет TM5 0.12 (Basic Preset). Безусловно, от всех ошибок мы не сможем избавиться, и для этого нам нужен будет следующий шаг.

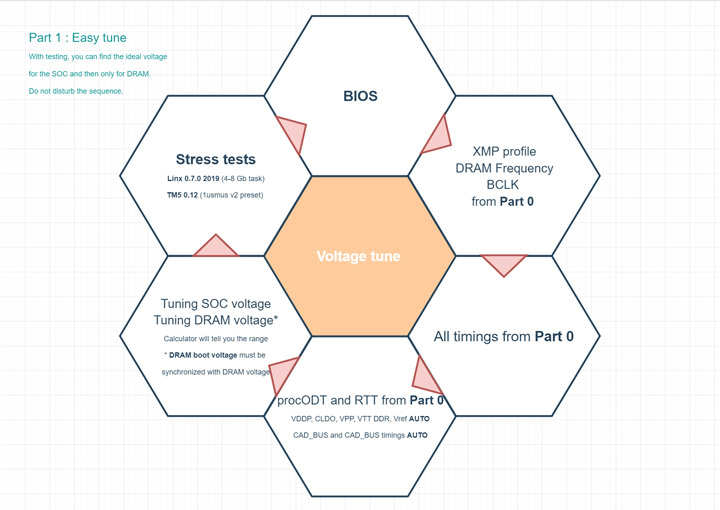

Цель следующего шага — поиск самого оптимального напряжения для DRAM и SOC, при которых система будет иметь минимальное кол-во ошибок. Сначала подбираем напряжение для SOC, а затем для DRAM (калькулятор вам подскажет диапазон). Для отлова ошибок используем тестовый пакет TM5 0.12 (Basic Preset).

В половине случаев вы можете на данном этапе получить полностью стабильную систему. Если тестовый пакет TM5 0.12 не находит ошибок, то вы должны увеличить спектр тестовых программ для проверки стабильности. Вы можете использовать LinX, HCI, Karhu, MEMbench и другие программы. В случае если вышеописанные утилиты нашли ошибку, то вам стоит перейти к следующему шагу, отладочному.

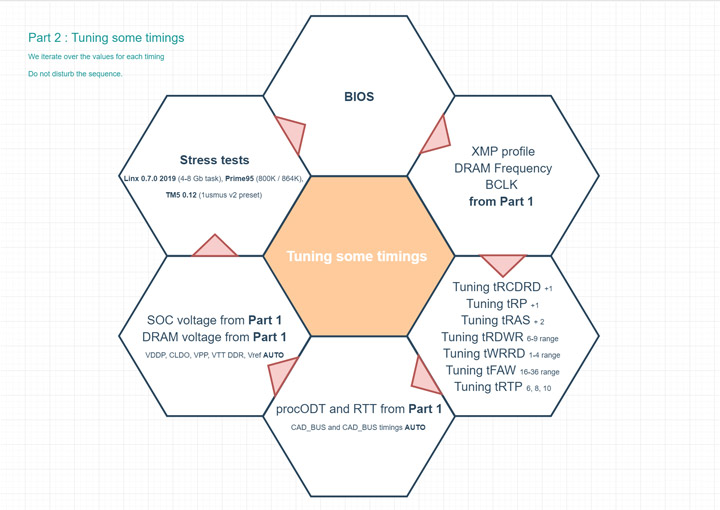

На отладочном шаге главная цель — это изменение определенных таймингов, указанные на иллюстрации ниже.

На данном этапе вы должны проверить по очереди влияние каждого тайминга на стабильность системы. Примечание: я не рекомендую изменять все задержки сразу, постарайтесь набраться терпения. Если тестируемый тайминг никак не улучшает ситуацию, мы его возвращаем на место и проверяем по списку следующую задержку.

На этом шаге основной инструктаж по отладке системы для простых пользователей заканчивается. Дальнейшие шаги я могу посоветовать более опытным оверклокерам, которые знакомы с разгоном достаточно давно.

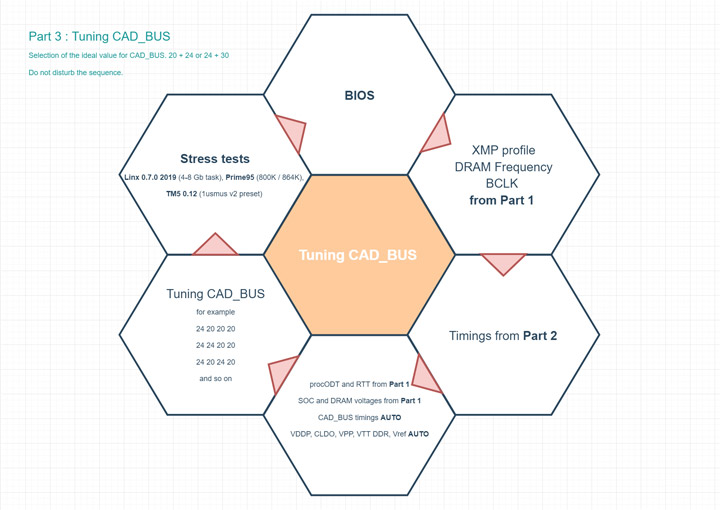

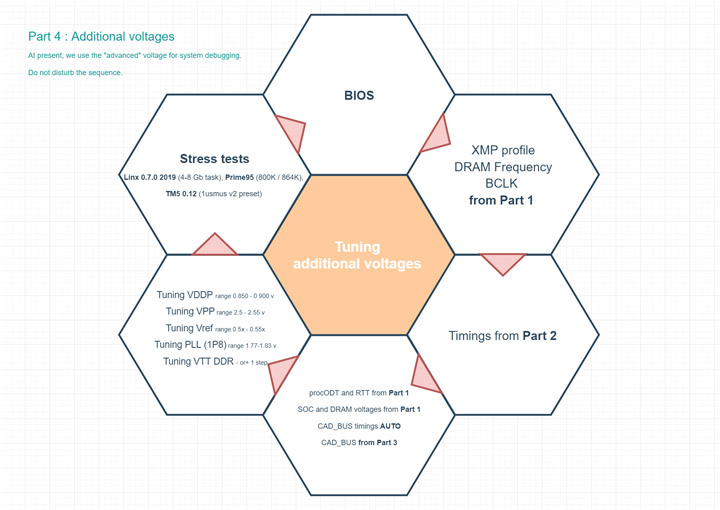

Тонкая настройка CAD_BUS

и корректировка дополнительных напряжений.

На каждой иллюстрации присутствуют списки параметров, которые мы используем или изменяем. Эти списки я сформировал так, чтобы более приоритетные настройки, которые могут помочь улучшить стабильность, вы проверили первыми. Безусловно, вы можете пойти своей дорогой, четких правил и закономерностей нет.