Основные операции DRAM

Существует пять основных операций (или четыре, если объединить чтение и запись в одну), которые необходимо выполнить при доступе к данным в DRAM.

Активация открывает одну из строк DRAM в банке и копирует данные из открытой строки в буфер строк.

Восстановление гарантирует, что заряд, который расходуется из каждой ячейки в строке DRAM во время активации, восстанавливается до полного уровня, чтобы предотвратить потерю данных.

Чтение и запись могут выполняться после копирования данных активированной строки в буфер строк.

Precharge освобождает данные из буфера строк, когда контроллер памяти выполняет чтение и запись в активированную строку, и подготавливает банк для активации другой строки.

Из них задержка доступа DRAM в основном состоит из задержки трех операций: активация, восстановление и предварительная зарядка.

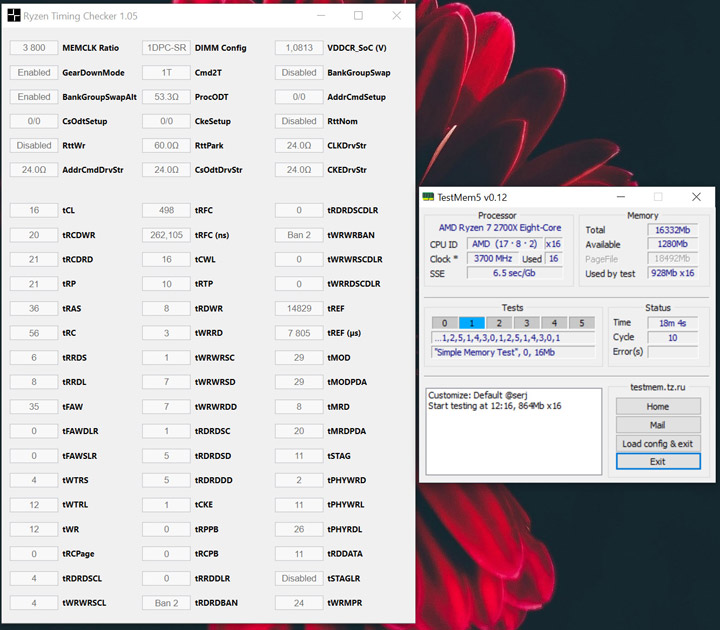

На рисунке выше показана временная шкала команд, выполненных для чтения (вверху) или записи (внизу) для одной строки данных кэша. Контроллер памяти выдает четыре команды: (1) ACT (активировать), (2) READ или (3) WRITE и (4) PRE (предварительная зарядка). Обратите внимание, что восстановление не имеет явной команды, а вместо этого запускается автоматически после команды ACT. Время, затрачиваемое на каждую операцию, определяется набором временных параметров, которые определяются поставщиками DRAM. Хотя каждая команда работает с гранулярностью строк, для простоты мы описываем, как операции DRAM влияют на одну ячейку DRAM.

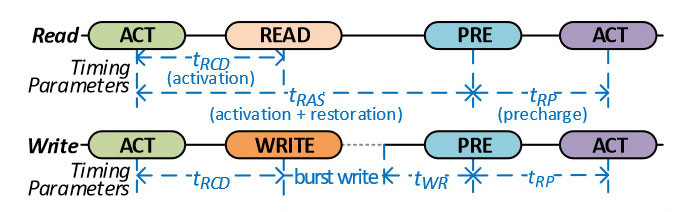

В начальном предварительно заряженном состоянии (1) битовая линия поддерживается на уровне напряжения VDD / 2, где VDD — полное напряжение питания DRAM. Линия слова находится в 0 В, и поэтому битовая линия отключена от конденсатора. После того, как контроллер памяти выдает команду ACT (2), словосочетание повышается до Vh, тем самым соединяя конденсатор ячейки DRAM с разрядной линией. Так как в этом примере напряжение на конденсаторе выше, чем на разрядной линии, заряд поступает на разрядную линию, повышая уровень напряжения до VDD / 2 + δ. Этот процесс называется разделением заряда. Затем усилитель считывания измеряет отклонение на битовой линии и соответственно усиливает это отклонение (3). Эта фаза, называемая чувственным усилением, в конечном итоге приводит уровень напряжения разрядной линии и ячейки к исходному состоянию напряжения ячейки (в данном примере VDD).

Как только усилитель считывания достаточно усилил данные в битовой линии (например, уровень напряжения достигнет 3VDD / 4), контроллер памяти может выдать команду READ или WRITE для доступа к данным ячейки в буфере строк. Время, необходимое для достижения этого состояния (3) после команды ACT, задается параметром синхронизации tRCD, как показано на первом рисунке. После того, как команда READ или WRITE введена, фаза чувствительного усиления продолжает управлять напряжением на битовой линии (4), пока уровень напряжения битовой линии и ячейка не достигнут VDD. Другими словами, исходный уровень заряда ячейки полностью восстанавливается до исходного значения для READ или корректно обновляется до нового значения для WRITE.

Для запросов на чтение DRAM задержка для ячейки, которая будет полностью восстановлена после ACT, определяется параметром синхронизации tRAS. Для запросов записи DRAM время, необходимое для полного обновления ячейки, определяется tWR. После восстановления битовая линия может быть предварительно заряжена с помощью команды PRE, чтобы подготовить подмассив для будущего доступа к другой строке. Этот процесс отключает ячейку от разрядной линии путем понижения напряжения на словарной линии. Затем он сбрасывает напряжение разрядной линии до VDD / 2. Время завершения операции предварительной зарядки определяется параметром синхронизации tRP.

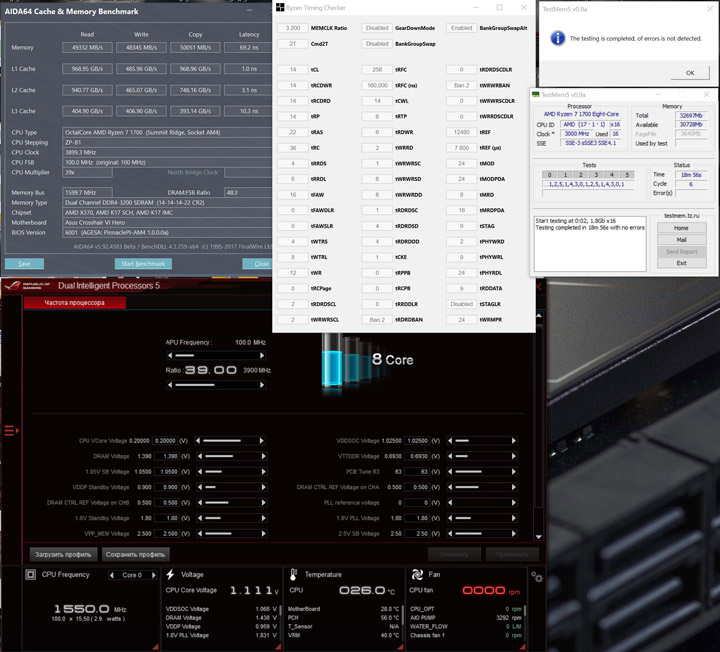

Значения tRCD и tRAS могут быть значительно ниже, чем в даташитах. Как так?

Обычные микросхемы DRAM выполняют операции активации и восстановления с использованием фиксированной задержки, которая определяется значением параметров синхронизации, показанных на первом изображении. Однако существуют способы, с помощью которых задержки для активации и восстановления могут быть уменьшены путем использования текущего уровня заряда ячейки. Если элемент имеет высокий уровень заряда, соответствующий процесс возмущения напряжения на битовой линии во время активации происходит быстрее, и, следовательно, усилителю считывания требуется меньше времени для достижения состояний 3 и 4 на втором изображении. «ChargeCache» — это современный механизм, который использует эту информацию для безопасного уменьшения временных параметров tRCD и tRAS для сильно заряженной ячейки.

ChargeCache отслеживает строки, к которым недавно был получен доступ, что означает, что их ячейки имеют высокий уровень заряда, поскольку с момента последнего восстановления ячеек до полного уровня заряда прошло только короткое время. Поэтому, если недавно активированная строка снова активируется в течение короткого интервала времени (например, 1 мс), ChargeCache использует более низкие значения tRCD и tRAS для строки, что уменьшает общую задержку доступа к DRAM. Аналогичный подход может быть применен для уменьшения времени восстановления. В обычном чипе DRAM каждая команда ACT запускает операцию восстановления, которая полностью восстанавливает уровень заряда ячеек в активированном ряду. Аналогично, каждая операция обновления полностью восстанавливает уровень заряда элемента в фиксированный интервал времени (каждые 64 мс в DDRx DRAM).

Существует также механизм Restore Truncation, который частично восстанавливает уровень заряда ячейки ровно настолько, чтобы сохранять правильные данные — до следующего обновления ячейки. Одним из элементов управления для этого механизма является время tWR и tRAS.

Некоторые предустановки, опубликованные в моей статье, используют эти механизмы, поэтому я советую вам забыть о типичных формулах, которые вы можете найти в Интернете.

Выводы

Поскольку элемент DRAM состоит из конденсатора, элемент теряет заряд, даже когда к нему нет доступа. Чтобы предотвратить потерю данных, DRAM должен выполнять периодические операции обновления для всех ячеек. Операция обновления возвращает уровень заряда ячейки к ее полному значению.

Современные микросхемы памяти позволяют устанавливать агрессивные временные интервалы благодаря механизму Restore Truncation и ChargeCache.

Микросхемы SDRAM в некотором смысле позволяют выполнять третью и четвертую операции параллельно. Если быть точным, команда перезарядки линии PRECHARGE может быть отправлена за определенное количество тактов x до момента, когда был выпущен последний элемент данных запрошенного пакета, не опасаясь возникновения «сломанной» ситуации в переданном пакете (последнее произойдет, если команда PRECHARGE отправит команды READ с периодом времени меньше x).

Чтобы предотвратить потерю данных в ячейках, вы можете увеличить напряжение DRAM или изменить временные характеристики, которые отвечают за предварительную зарядку и обновление. Регулировка tRP и tRFC будет иметь наибольшее влияние, tWR и tRTP также могут помочь. Я не советую поднимать значение tWR выше 12.

tRC> = tRAS + tRP. Для большинства случаев это должна быть оптимальная формула.

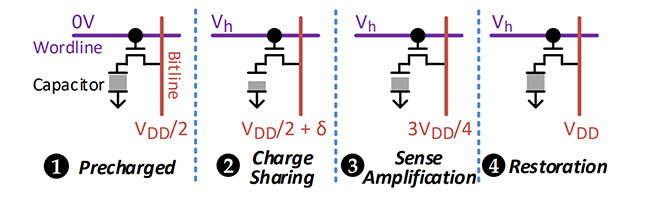

tRAS = tRCD + tCL. У меня нет четкого определения для этого тайминга, оно может быть равно tRCD + tCL, но иногда значительно ниже из-за механизмов, перечисленных выше. Также не стоит забывать и о запасе, пределы которого определяются чисто экспериментальным путем, поскольку каждый чип имеет различные характеристики ячеек. Вот вам один из примеров.

Для высоких частот я использую формулу из первого рисунка. tRAS = tRCD + tBL + tWR, где tWR тюнингованное, которое равно 12 или 10. tBL для DDR4 всегда равен 4, но контроллер может использовать и 2.

Пример: