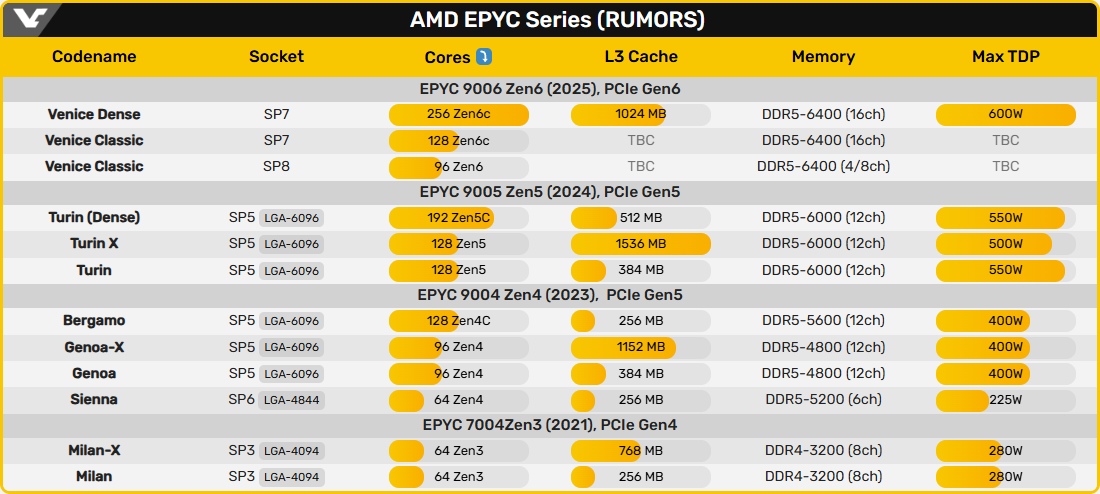

От неофициальных источников поступили новые подробности о следующем поколении серверных процессоров AMD EPYC, известном под кодовым именем Venice. В этих CPU компания перейдёт на микроархитектуры Zen 6 и Zen 6c, а для их производства будет использована 2‑нм технология TSMC, чем уже успела похвастаться глава «красного» чипмейкера.

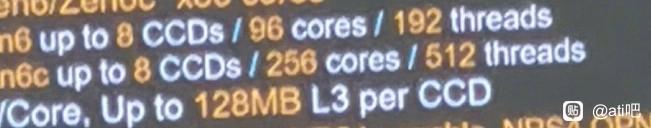

Свежие утечки информации раскрывают некоторые важные особенности будущих CPU EPYC 9006. В частности, подтверждается использование восьми микросхем Core Complex Die (CCD) с x86-ядрами. Это значит, что процессоры с архитектурой Zen 6 благодаря 12-ядерным чиплетам CCD смогут предложить до 96 ядер/192 потоков. В то же время CPU Zen 6c получат 32-ядерные чиплеты, то есть в их арсенале будет 256 ядер/512 потоков.

В документах AMD также упоминается до 128 МБ кэш-памяти третьего уровня в одной микросхеме Core Complex Die. То есть при наличии восьми чиплетов CCD суммарный объём L3-кэша у таких процессоров составит 1 ГБ. Ранее для достижения таких показателей «красным» приходилось использовать технологию 3D V‑Cache.

Вместе с новыми процессорами дебютирует серверная платформа Socket SP7, которая принесёт поддержку 16-канальной оперативной памяти DDR5. Для CPU в этом конструктивном исполнении будет характерен TDP до 600 Вт. AMD также готовит более простую платформу Socket SP8. Она будет поддерживать 96-ядерные процессоры Zen 6 с уровнем TDP около 350–400 Вт и, вероятно, 8‑канальную память DDR5.

Официальные подробности о серверных чипах AMD EPYC 9006 (Venice), по мнению зарубежных коллег, компания может раскрыть на презентации Advancing AI в июне.

Что касается потребительских CPU Zen 6, то они тоже должны перейти на использование 12-ядерных микросхем CCD. Благодаря этому будущие топовые процессоры для настольных ПК получат 24-ядерную/48-поточную конфигурацию. Будем надеяться, что десктопные процессоры Zen 6 продолжат использовать платформу AMD AM5.

Источники:

WCCFTech

VideoCardz